Electromagnetic interference (EMI) failures are rarely random. In most cases, they are the direct result of preventable PCB design decisions made months earlier.

For established businesses, an EMI failure means delayed product launches, damaged brand credibility and unexpected re-spins. For startups, it can mean burned runway and missed investor milestones. The uncomfortable truth? Most EMI problems are designed into the board long before compliance testing.

If you’re developing electronics products, here are the most common PCB design mistakes that trigger EMI failures — and how to eliminate them early.

Introduction to EMI in PCB Design

Electromagnetic interference occurs when unwanted electromagnetic energy disrupts circuit operation or exceeds regulatory emission limits. Every PCB radiates. The question is whether it radiates within acceptable limits.

Modern products combine:

Fast switching regulators

High-speed digital interfaces

Dense layouts

Multiple power domains

Without deliberate design for EMI control, emissions are inevitable.

Compliance testing (CE, FCC, CISPR) doesn’t “fix” EMI. It simply measures how well you designed against it.

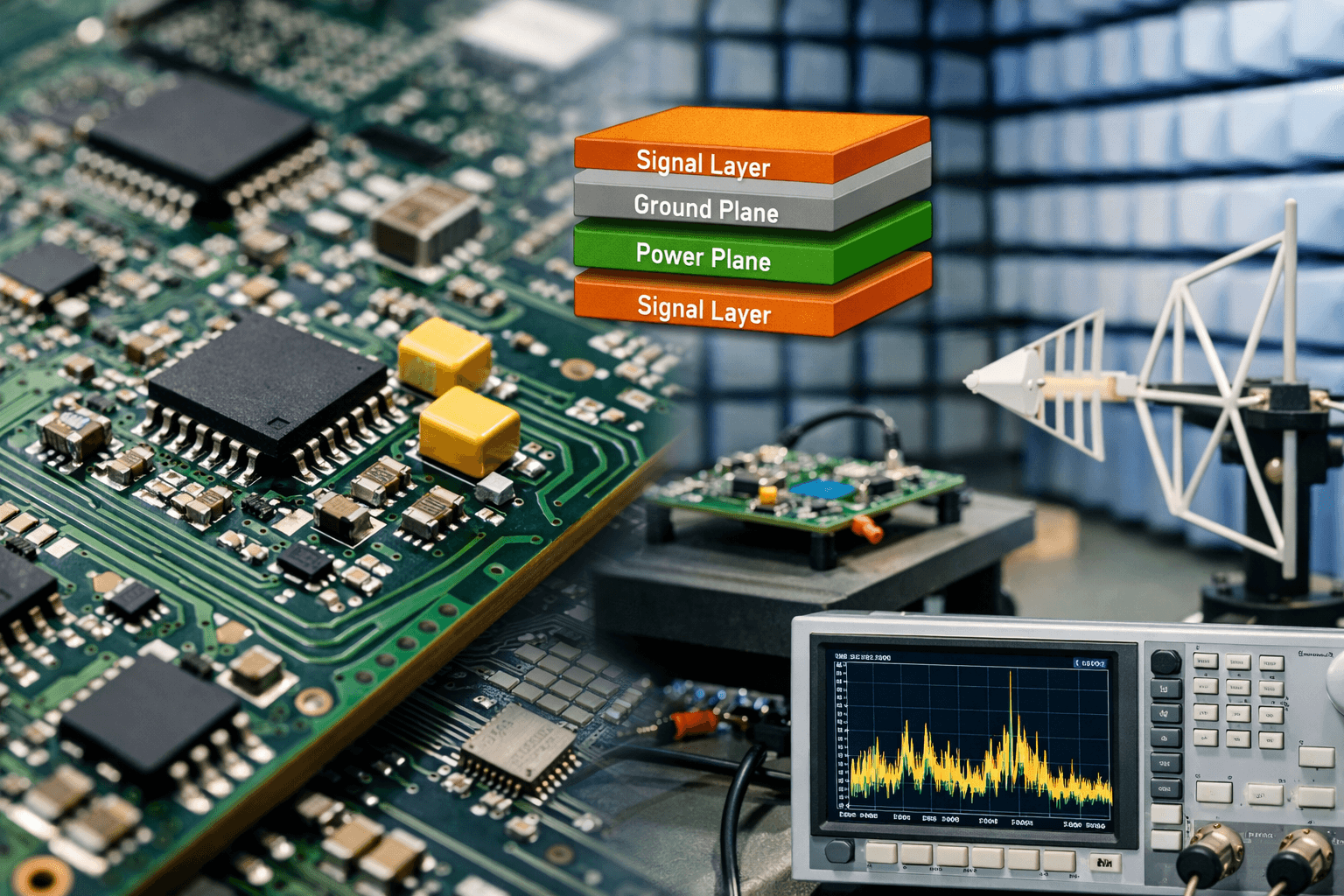

Poor Stack-Up Planning

Your PCB stack-up is the foundation of EMI performance. If it’s wrong, no amount of filtering will save you.

Inadequate Ground and Power Plane Configuration

A common mistake is treating stack-up as a manufacturing detail instead of an electrical design decision.

A robust stack-up typically includes:

Continuous reference planes adjacent to signal layers

Tight coupling between power and ground planes

Symmetry to reduce warping and impedance variation

Without proper reference planes, return currents spread unpredictably, increasing loop area and radiated emissions.

Missing Dedicated Return Paths

High-frequency currents always take the path of least impedance — not least resistance. If you don’t provide a clear return path directly under the signal trace, the current will find one. That detour increases radiation.

How Layer Order Impacts Radiated Emissions

Signals routed next to solid ground planes produce significantly lower EMI than those routed over split planes or thin pours. Stack-up decisions directly control field containment.

Broken or Fragmented Ground Planes

A solid ground plane is your best EMI suppression tool — and designers routinely break it.

Why Continuous Ground Planes Matter

Ground planes:

Provide low-impedance return paths

Reduce loop area

Contain electric fields

Lower impedance at high frequencies

Cut that plane, and you force return currents to reroute.

The Hidden Danger of Plane Splits

Splitting analogue and digital grounds without understanding return current behaviour often increases EMI instead of reducing it. High-frequency currents do not respect your labelling.

High-Frequency Return Current Behaviour

At high frequencies, return current flows directly under the signal trace. If a gap exists, the current detours — forming a large loop antenna.

Excessive Loop Areas in Signal Routing

Loop area equals radiation. This is not optional physics.

Loop Area and Magnetic Field Radiation

Any current loop generates a magnetic field. Increase the loop area and emissions increase proportionally.

Typical causes:

Poor trace-to-ground referencing

Long signal runs without nearby return

Connector transitions without stitching vias

Poor Placement of Return Paths

Routing a signal across layers without stitching vias to maintain reference continuity creates discontinuities — prime radiation points.

Reducing Loop Area in High-Speed Designs

Keep:

Signals close to reference planes

Via transitions tightly stitched

Power loops (especially switching regulators) extremely compact

Improper Decoupling and Bypass Capacitor Placement

You can choose the perfect capacitor value and still fail EMI.

Why Placement Matters More Than Value

A decoupling capacitor placed 20 mm away from the IC is ineffective at high frequencies. Inductance dominates.

Place capacitors:

As close as physically possible to power pins

With minimal loop area

With short, wide connections to ground

High-Frequency Current Demands

Digital ICs draw sharp current spikes. If local decoupling is poor, those spikes travel across the board, turning planes into radiating surfaces.

Common Decoupling Layout Errors

Long thin traces

Shared vias for multiple capacitors

Routing before placing capacitors

Placement must come first.

Long High-Speed Trace Routing

Fast edges create broadband emissions.

Transmission Line Effects and EMI

Once trace length approaches a fraction of the signal rise time wavelength, it behaves as a transmission line. Reflections increase ringing. Ringing increases emissions.

Uncontrolled Impedance Problems

Ignoring impedance control leads to:

Reflections

Overshoot

Increased spectral content

This directly impacts EMI performance.

Minimising Radiation from Fast Edges

Control impedance

Use proper terminations

Shorten trace length

Avoid unnecessary stubs

Poor Component Placement Strategy

EMI control begins with placement — not routing.

Functional Zoning Principles

Partition the board into:

Noisy power section

Digital processing section

Sensitive analogue section

I/O interface zone

Don’t scatter these randomly.

Separating Noisy and Sensitive Circuits

Switching regulators next to analogue front ends is a predictable failure mode.

Early-Stage EMI Planning

If EMI is considered after routing, it’s too late. Placement must reflect current flow paths from day one.

Inadequate Grounding of Connectors and Cables

Cables are antennas. Full stop.

Cables as Unintentional Antennas

Any high-frequency noise reaching a cable can radiate efficiently. Poor connector grounding makes compliance nearly impossible.

Shield Termination Best Practices

Shield terminations should:

Bond 360° to chassis ground

Minimise pigtails

Avoid long ground wires

Chassis Ground vs Signal Ground Confusion

Improper bonding between chassis and signal ground creates unintended current paths.

Lack of Controlled Impedance Design

At higher data rates, this is not optional.

Why Impedance Mismatch Increases Emissions

Reflections increase voltage peaks and ringing, generating higher harmonics.

Differential Pair Routing Errors

Common mistakes:

Unequal trace lengths

Poor spacing control

Crossing plane splits

The Role of PCB Stack-Up Calculations

Impedance depends on:

Dielectric thickness

Trace width

Copper thickness

Plane proximity

If you didn’t calculate it, you don’t control it.

Ignoring Power Integrity

Power integrity and EMI are inseparable.

Switching Regulators as EMI Sources

Fast switching edges and high di/dt loops are primary emission sources.

Minimise:

Hot loop area

Gate drive trace length

Input capacitor distance

Poor Power Plane Layout

Large uninterrupted noisy power areas radiate more than tightly coupled planes.

Managing Ripple and Transient Noise

Ripple currents must be contained locally. If they spread, emissions increase.

Incorrect Use of Ground Fills and Stitching Vias

More copper is not automatically better.

When Copper Pours Make Things Worse

Floating copper islands act as antennas. If a ground fill is not well connected, remove it.

Via Fencing for Emission Control

Stitching vias around board edges and high-speed areas help contain fields and reduce edge radiation.

Edge Radiation Prevention Techniques

Fields tend to escape at PCB edges. Via stitching and tight plane coupling reduce leakage.

Overlooking Signal Rise and Fall Times

Frequency is not the only factor — edge rate matters more.

Why Fast Edges Cause EMI Problems

A 10 MHz clock with 1 ns edges contains frequency components far beyond 10 MHz.

Slew Rate Control Techniques

Where possible:

Slow down edges

Use series resistors

Select drivers with controlled rise times

Termination Strategies That Reduce Emissions

Proper termination reduces ringing and spectral spread.

Poor Isolation Between Analogue and Digital Sections

Mixed-signal boards are particularly vulnerable.

Mixed-Signal PCB Challenges

Digital noise coupling into analogue circuits leads to both functional and compliance failures.

Proper Partitioning Without Splitting Planes

Avoid unnecessary ground splits. Instead:

Use placement zoning

Control return paths

Use filtering at boundaries

Managing High-Frequency Coupling

Short return paths and careful routing reduce cross-domain interference.

Neglecting Pre-Compliance Testing

Waiting for official lab testing is financially reckless.

Why Lab Testing Shouldn’t Be the First EMI Check

By the time you reach formal testing:

Tooling is paid

Firmware is stable

Marketing has launch dates

A failure here is expensive.

Cost Implications of Late Discovery

A single PCB re-spin can cost:

Engineering time

Manufacturing delay

Lost opportunity

Practical Pre-Compliance Strategies

Near-field probing

Bench-level spectrum analysis

Early radiated emission scans

Designing Without EMC Standards in Mind

Compliance is not a post-design activity.

Key Standards Overview

Depending on your market, you’ll likely face:

CE requirements

FCC regulations

CISPR emission limits

Each defines acceptable emission levels.

Design for Compliance from Day One

Understand your target market before layout begins. Design margins into your architecture.

Building EMI Resilience Into Your Development Process

Create internal design reviews focused specifically on:

Return paths

Loop areas

Power integrity

Connector grounding

Practical EMI Design Checklist for Engineering Teams

Before release to manufacturing:

Verify stack-up and reference planes

Inspect return path continuity

Confirm decoupling placement

Review switching regulator layout

Check impedance calculations

Validate shielding and connector grounding

Conduct pre-compliance scans

If these steps aren’t formalised, EMI failures become likely rather than possible.

Conclusion: Designing PCB Layouts That Pass EMI First Time

EMI failures are rarely mysterious. They are usually the result of overlooked fundamentals in PCB design.

For startups, EMI mistakes consume runway. For established companies, they delay revenue and damage credibility. In both cases, prevention is cheaper than correction.

The strategic approach is simple:

Design stack-up intentionally

Control return paths

Minimise loop areas

Contain switching currents

Test early

EMI performance is not about adding filters at the end. It’s about designing intelligently from the first schematic capture.

If your organisation treats EMI as a late-stage hurdle rather than a design discipline, that’s the blind spot.

Fix that — and your next product stands a far better chance of passing first time.

0 Comments